#### **PAPER • OPEN ACCESS**

# Design of Digital Clock Manager Using Tunable BFD–True Random Number Generator

To cite this article: A Chaitanya Krishna et al 2021 J. Phys.: Conf. Ser. 1964 062003

View the article online for updates and enhancements.

### You may also like

- Quantum cryptography and combined schemes of quantum cryptography communication networks A.Yu. Bykovsky and I.N. Kompanets

- Security analysis of a random number generator based on a chaotic hyperjerk system

Kaya Demir and Salih Ergün

- <u>Survey, taxonomy, and methods of QCAbased design techniques—part II:</u> <u>reliability and security</u> Mohammad Mudakir Fazili, Mohsin Fayaz Shah, Syed Farah Naz et al.

#### The Electrochemical Society Advancing solid state & electrochemical science & technology

## 242nd ECS Meeting

Oct 9 – 13, 2022 • Atlanta, GA, US Early hotel & registration pricing ends September 12

Presenting more than 2,400 technical abstracts in 50 symposia

The meeting for industry & researchers in

ENERGY TECHNOLOG

ECS Plenary Lecture featuring M. Stanley Whittingham, Binghamton University Nobel Laureate – 2019 Nobel Prize in Chemistry

This content was downloaded from IP address 119.235.48.134 on 04/08/2022 at 10:15

# **Design of Digital Clock Manager Using Tunable BFD-True Random Number Generator**

A Chaitanya Krishna<sup>1\*</sup>, Ch Priyanka<sup>2</sup>, and Divya Gampala<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, St. Martin's Engineering College, Secunderabad, Telangana, India <sup>2</sup>Department of Electronics and Communication Engineering, CMR Engineering College, Hyderabad, Telangana, India Email: \*drchaitanyaece@smec.ac.in,

Abstract. By demanding authentication exercises for example communications, electronic cash frameworks, plate encryption, the cryptographic frameworks have become a core aspect in our daily lives. Random numbers are an significant factor in strengthening and anchoring the protection of e-mail messages used in multiple encryption applications, including key ages, encryption, convention coverage, web wagering. Random flight numbers for basic mystery keys are basic to the protection of criphotographical calculations. In a variety of cryptographic systems, actual random number generators (TRNGs), The part has been incorporated, including PIN / secret word age, validation agreements, key age, random cushions and age of nunce. The circuit uses an undetermined random mechanism as a fundamental source, largely as electric commotion. Programmable field door arrays (FPGAs) are the optimal stage for the success of equipment that offers substantial safety conditions. The TRNG suggested is subject to the Xilinx-FPGA Bit Recurrence Recognition Guideline.

Keywords: Application of the Real Random Number Generator (TRNG), Cryptography (FPGA), Dynamic Reconfiguration Port (DRP), Field programmable gate arrays (FPGA).

#### 1. Introduction

At present, world security is highly important, and cryptography now plays an imperative role in PC and device management security. The organisation of data concealing techniques is cryptography [2]. It is used in some places to anchor data and information as a feature of security conventions. Correspondence, like the Internet and numerous correspondence methods, has brought in security risks. Subsequently, cryptography guarantees critical hazards by supplying information, i.e. supplying a range of means and techniques to turn information into a non-understandable system [4]. The essential point of cryptography is that the unapproved client cannot got to information. The proposed DPWM incorporates an asynchronous (counter-based) block for improved resolution without raising the clock frequency excessively [9]. The substance of the information edges ought to be encoded with positive example. Another appeal is to ensure the originator of the message is aware of the information in a reliable manner. In view of the fact that cryptographing systems depend on some details [5], identified by designated customers and uncommon by other and sometimes odd strings, to warrant their flight (e.g., keys, salts, nouns, issues, introductory vectors and other one-time quantities) [1] arbitrary numbers are fundamental for protection.

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1

#### 2. Related Work

2.1. Single Phase BFD-TRNG Model:

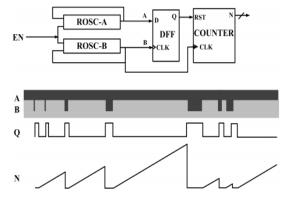

In accordance with Figure 1 the configuration and functionality of (one stage) the BFD-TRNG can be described [6] as follows.

Figure1. Single process BFD – TRNG architecture

- The circuit contains two semi traceable, equivalent development and place ring oscillator (the circuit is called ROSCA and ROSCB). Due to its physical haphazards, from the results of a number of processes involved with the manufacture of deep sub-micron CMOS, One waver is marginally faster than the other, STRILL. The artist also recommended the use of trimming condensers to further change the frequencies of the oscillator [7].

- Performance of a RO with D flip slum (DFF), is used to measure another's output. If the assertion is all inclusive, the ROSCA yield will be increased the clock contribution of the DFF and the yield of the ROSCB shall be compared to that of the DFF [8].

- As the oscillator flag moves higher, it increases and overwhelms the more rapid motion at these intervals in the levels. Increased jitters allow these moments, called "beat frequency intervals" to occur indiscriminately interim. Therefore, in some irregular situations, the DFF yields rationale 1.

- DFF-controlled counter raises in the intermediate time of beat recurrence and is reset by way of DFF yield 1 rationale. The free running counter rate raise in each check interim to several pinnacle figures until reset due to the erratic jitter [10].

- The counter yield shall be tested by a measure clock before achieving its full appreciation.

- The inspected reaction is then serialized to acquire the irregular piece stream [11].

#### 3. Proposed Tunable BFD-TRNG

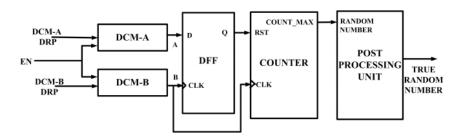

The design of the proposed digital clock manager with tunable BFD-TRNG is seen in figure 2. The DCM crudding is parameterized to allow marginally characteristic recurrences with the modification of some of the arguments called M and D, which are known respectively as multiplication and division factors. In this implementation, the randomness source is introduced as a jitter in the circuitry of DCM [12]. This DCM modules permit substantial designer command via the clock waveforms, and the requirement of primary calibration is eliminated with their utilization [3]. The tunability is developed using DPR and DRP ports as the basis for a DCM flying claim, which allows the current BFD-TRNG a higher degree of versatility in the draught. The distinction in the recurrences is taken by using DFF two rendered clock signals. When one cycle is finished, the DFF adjusts with a faster than a slower oscillator. As DFF is updated, one of the clock signals controls and is reset and thus increases the generated random numbers. The end three LSBs of the full number value are reached to illustrate the properties of good randomness.

**1964** (2021) 062003 doi:10.1088/1742-6596/1964/6/062003

Figure2. Total architecture of the planned tunable BFD-TRNG Digital Clock Manager

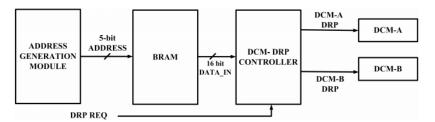

Figure 3 displays the tuning circuit block diagram. Goal clock frequency choices are made by a parameter range that was initially chosen. Both counter and jitter random values are correlated with selected M and D values, which allows it to tun the proposed TRNG with the use of the predetermined values contained in M and D. As non-deceptive DPRs are discovered to be a potential circuit threat[6], unification for the M and D values for each DCM is calculated by pre-deciding during the design phase and are held securely on the BRAM chip block in FPGA. In reality, there are a range of choices for clock generation. The hard PLL macros used on Xilinx FPGAs or DCMs can be used once[13].

Figure3. Tuning circuitry block diagram.

In many logical applications, astonishing arbitrary numbers are fundamental, particularly for reenactments from Monte Carlo. Provided the advantages of superior and reproducibility, the PRNG generators are normally obtained in these recreations in view of straight replicates over F2. The Mersenne Twister (MT) is a popular F2 straight PRNG with a considerable amount and a wide equidistribution radius. However, MT still has some inconveniences. For example, one crucial problem is the weak execution and a lengthy chance to rebound from a starting state of zero-overabundance. To address this crisis, the well fitted measurement of an important lot direct (WELL) is suggested Figure 3 displays the tuning circuit block diagram. Goal clock frequency choices are made by a parameter range that was initially chosen [14]. Both counter and jitter random values are correlated with selected M and D values, which allows it to tun the proposed TRNG with the use of the pre-determined values contained in M and D. As non-deceptive DPRs are discovered to be a potential circuit threat [6], unification for the M and D values for each DCM is calculated by pre-deciding during the design phase and are held securely on the BRAM chip block in FPGA. In reality, there are a range of choices for clock generation. The hard PLL macros used on Xilinx FPGAs or DCMs can be used once. In any case, there is no need of machinery. A succinct proslog of its item used in the WELL measurement was given by Ukalta Engineering Company [15]. Nevertheless, it only executes a single example Two loops any time, and no fundamental interest points are found. We suggest more acquisitive structure, which limits the use of BRAMs from four to two, with comparable results. The cumulative asset used is similarly reduced by half and the first structure. In addition, in view of the new building, we intend to parallel the yield of a product / equipment system [8]. We make the associated obligations in particular.

1) Construction of WELL asset efficient equipment with one example per cycle throughput.

- 2) A dedicated, 6R/2W WELL-ram arrangement which can be used for six reads and two writings with little overhead properties simultaneously in one loop.

- 3) A parallel erratic product / equipment scheme.

### 4. Simulation Results

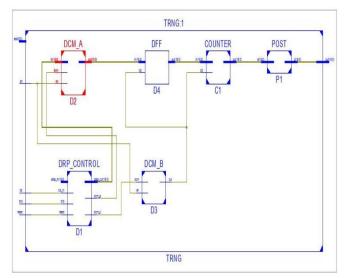

With the modification of some of the arguments called M and D, which are known as multiplication and division factors, the DCM crud ding is parameterized to allow marginally characteristic recurrences. The source of randomness is implemented in this implementation as a jitter in the DCM circuitry. Figure 4 shows the energy consumption report of the suggested technique, Figure 5 shows the delay (timing) report of the suggested technique and Figure 6 shows the design overview report of the suggested technique. Figure 7 show RTL Schematic and the performance of the proposed method respectively and output wave form shown in figure 8.

| I  |           |   | On-Ch    | ip H | Pow | er Sumr | naı | ry        |   |             |     |

|----|-----------|---|----------|------|-----|---------|-----|-----------|---|-------------|-----|

| I  | On-Chip   | I | Power (: | mW)  | I   | Used    | I   | Available | I | Utilization | (%) |

| 1  | Clocks    | 1 | 1        | .30  | 1   | 3       | 1   |           | 1 |             |     |

| l  | Logic     | 1 | 0        | .00  | 1   | 10      | 1   | 11776     | 1 |             | 0   |

| I  | Signals   | 1 | 0        | .00  | 1   | 20      | 1   |           | 1 |             |     |

| I  | IOs       | 1 | 0        | .00  | 1   | 20      | 1   | 372       | 1 |             | 5   |

| I  | Quiescent | 1 | 31       | . 52 | 1   |         | 1   |           | 1 |             |     |

| I. | Total     | 1 | 32       | .83  | 1   |         | 1   |           | 1 |             |     |

#### Figure4. Power report

| )ffset:                           | et: 6.769ns (Levels of Logic = 2)                                        |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Source:                           | C1/out 7 (FF)                                                            |  |  |  |  |  |  |  |  |  |  |

| Destination:                      | out<8> (PAD)                                                             |  |  |  |  |  |  |  |  |  |  |

|                                   |                                                                          |  |  |  |  |  |  |  |  |  |  |

| Source Clock:<br>Data Path: C1/ou | t_7 to out≺8>                                                            |  |  |  |  |  |  |  |  |  |  |

|                                   |                                                                          |  |  |  |  |  |  |  |  |  |  |

| Data Path: C1/ou                  | it_7 to out<8><br>Gate Net                                               |  |  |  |  |  |  |  |  |  |  |

| Data Path: C1/ou<br>Cell:in->out  | ut_7 to out<8><br>Gate Net<br>fanout Delay Delay Logical Name (Net Name) |  |  |  |  |  |  |  |  |  |  |

### Figure5. Timing report

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |  |  |

| Number of Slices                              | 9    | 5888      | 0%          |  |  |  |  |  |

| Number of Slice Flip Flops                    | 10   | 11776     | 0%          |  |  |  |  |  |

| Number of 4 input LUTs                        | 17   | 11776     | 0%          |  |  |  |  |  |

| Number of bonded IOBs                         | 20   | 372       | 5%          |  |  |  |  |  |

| Number of GCLKs                               | 1    | 24        | 4%          |  |  |  |  |  |

Figure6. Design Summary

#### **1964** (2021) 062003 doi:10.1088/1742-6596/1964/6/062003

Figure7. RTL Schematic

Figure8. Waveforms

#### 5. Conclusion

This paper innovated an FPGA-based implementation of enhanced fully digital tunable TRNG. Proposed technique operated using BFD principle and clock jitter with inherent correction of error potentialities. Our proposed TRNG employed the features of tunability for deciding the randomness degree, hence rendered a higher degree of feasibility for several applications. Further, all the NIST statistical tests also done by the proposed architecture.

#### References

- [1] D. Liu, Z. Liu, L. Li, and X. Zou, "A Low-Cost Low-Power Ring Oscillator-Based Truly Random Number Generator for Encryption on Smart Card", *IEEE Transactions on Circuits and Systems II: Express briefs*, vol. 63, no. 6, pp. 608-612, Jun. 2016.

- [2] A. P. Johnson, R. S. Chakraborty and D. Mukhopadhyay, "APUF enabled secure architecture for FPGA based IoT applications", *IEEE Transactions* on Multi-Scale Computing Systems, vol. 1, no. 2, pp. 110-112, Jun. 2015.

- [3] A. P. Johnson, R. S. Chakraborty and D. Mukhopadhyay, "A Novel Attack on a FPGA based True Random Number Generator", *10<sup>th</sup>Workshop on Embedded Systems Security*, Amsterdam, Netherlands, Oct. 2015.

- [4] A. P. Johnson, et al., "Fault Attack on AES via Hardware Trojan Insertion by Dynamic Partial Reconfiguration of FPGA over Ethernet",9<sup>th</sup> Workshop on Embedded Systems Security, New Delhi, India, Oct. 2014.

- [5] A. Rukhin, et al., "A Statistical Test Suite for Random and Pseudorandom Number Generators for Cryptographic Applications", *DTIC Document*, 2001.

- [6] N. Tang, et al., "True Random Number Generator circuits based on single- and multi-phase beat frequency detection", In Proceedings of Custom Integrated Circuits Conference, San Jose, CA, USA, *IEEE*, Nov. 2014.

- [7] J. V. Neumann, "Various Techniques used in Connection with Random Digits", *National Bureau* of Standards Applied Mathematics Series, vol. 5, Pergamon Press, Oxford, 1963.

- [8] Y. Li, P. Chow, J. Jiang, M. Zhang, and S. Wei, "Software/Hardware Parallel Long-Period Random Number Generation Framework Based on the WELL Method", *IEEE Transactions on Very Large-Scale Integration (VLSI) Systems*, vol. 22, no. 5, pp. 1054-1059, Mar. 2014.

- [9] Murugesan, R. and Madhusudhanan, R., 2009. FPGA based Digital Pulse Width Modulator with Time Resolution under 2 ns. *International Journal of MC Square Scientific Research*, 1(1), pp.33-38.

- [10] Human Muscle Mass Measurement through passive Flexible UWB-Myogram Antenna sensor to diagnose Sarcopenia ,SeshaVidhya, S., Rukmani Devi, S., Shanthi, K.G. Microprocessors and Microsystems, 2020, 79, 103284

- [11] Spectrum energy detection in cognitive radio networks based on a novel adaptive threshold energy detection method Sarala, B., Rukmani Devi, S., Sheela, J.J.J. Computer Communications, 2020, 152, pp. 1-723.

- [12] Tupparwar, S., & Mohankumar, N. (2021, January). A Hybrid True Random Number Generator using Ring Oscillator and Digital Clock Manager. In 2021 6th International Conference on Inventive Computation Technologies (ICICT) (pp. 290-294). IEEE.

- [13] Wang, F., Dai, M., Sun, Q., & Ai, L. (2021, March). Design and implementation of CMOSbased low-light level night-vision imaging system. In Seventh Symposium on Novel Photoelectronic Detection Technology and Applications (Vol. 11763, p. 117635O). International Society for Optics and Photonics.

- [14] Wang, F., Dai, M., Sun, Q., & Ai, L. (2021, March). Design and implementation of CMOSbased low-light level night-vision imaging system. In Seventh Symposium on Novel Photoelectronic Detection Technology and Applications (Vol. 11763, p. 117635O). International Society for Optics and Photonics.

- [15] Asif, M., Ali, I., Khan, D., Rehman, M. R. U., Pu, Y., Yoo, S. S., & Lee, K. Y. (2021). Design of High Performance Hybrid Type Digital-Feedback Low Drop-Out Regulator Using SSCG Technique. IEEE Access, 9, 28167-28176.